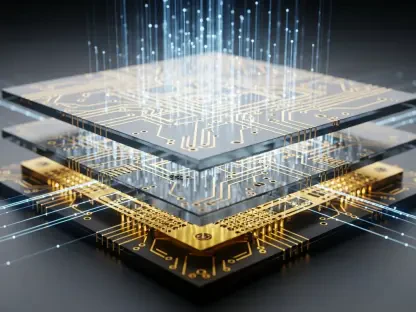

The recent advancements in semiconductor technology represent a significant stride in the field of artificial intelligence (AI) hardware, especially in the development of high-rise, three-dimensional (3D) chips. The traditional industry practice of increasing the number of transistors on a single silicon wafer is reaching its physical limits, prompting researchers and engineers to explore vertical stacking of semiconductor materials. This approach is analogous to transforming a ranch house into a high-rise, thereby significantly enhancing data handling and processing capabilities. The Massachusetts Institute of Technology (MIT) engineers have successfully developed a new method for fabricating multilayered chips that does not rely on traditional silicon wafer substrates while maintaining the integrity of the underlying circuitry at relatively low temperatures.

Overcoming Traditional Silicon Wafer Limitations

Challenges with Traditional Methods

Traditional methods in semiconductor fabrication have long relied on bulky silicon wafers to grow high-quality, single-crystalline semiconducting elements. This reliance poses significant challenges, particularly in the development of three-dimensional stackable chips. Historically, each semiconductor layer has required a thick silicon base, which inevitably slows down intra-layer communication and computation processes. In essence, these silicon layers act like wide pillars, limiting the efficiency and speed of data processing. MIT’s novel method addresses this challenge head-on by completely eliminating the need for silicon wafer substrates, thereby facilitating direct contact between multiple semiconducting layers.

By bypassing the traditional silicon base, MIT’s innovative approach not only enhances computational efficiency but also enables more compact and lightweight chip designs. Eliminating silicon substrates allows for a more seamless integration of the layers, optimizing data flow between them. This development could potentially revolutionize AI hardware by creating devices that are vastly more powerful and efficient. The implications of this breakthrough are far-reaching, potentially ushering in a new era where laptops and wearable devices boast computational capabilities that rival today’s supercomputers, alongside storage capacities comparable to modern data centers.

Breakthrough in Multilayered Chip Fabrication

According to Jeehwan Kim, Associate Professor of Mechanical Engineering at MIT and study author, this technical breakthrough could signal a new era for the semiconductor sector by enabling unprecedented stacking of chips without the constraints traditionally imposed by silicon wafers. This advancement results from extensive collaboration among an interdisciplinary team of experts, including first author Ki Seok Kim, additional researchers from MIT, and collaborators from Samsung Advanced Institute of Technology, Sungkyunkwan University in South Korea, and the University of Texas at Dallas. Their combined efforts have been meticulously documented in the prestigious journal Nature.

The profound implications of their work hinge on the seamless integration of multilayered chip designs at low temperatures without sacrificing the integrity or quality of the underlying circuitry. This method could potentially pave the way for AI hardware that is not only faster but also more energy-efficient. The reduction in manufacturing complexity and the elimination of high-temperature processes mean that the new approach could be more environmentally friendly and cost-effective. Thus, this breakthrough has the potential to dramatically shift the semiconductor industry’s landscape, fostering further innovations in technology development.

Transition-Metal Dichalcogenides: The Future of Semiconductors

Advantages of TMDs Over Silicon

In 2023, Kim’s group innovated a method for growing high-quality semiconducting materials on amorphous surfaces, mirroring the complex topography found in semiconducting circuitry of finished chips. Transition-metal dichalcogenides (TMDs) have emerged as promising candidates for the future of semiconductors, particularly for the fabrication of smaller, yet high-performance transistors. Unlike silicon, which tends to lose its semiconducting properties as it scales down to atomic levels, TMDs maintain their performance and integrity even at microscopic dimensions. This makes TMDs distinctly advantageous for advancing semiconductor technologies, particularly for applications requiring high efficiency and miniaturization.

The properties of TMDs lend themselves well to creating more scalable and powerful semiconductor devices. These materials can be grown on a variety of surfaces, including those with complex topographies, further enhancing their versatility. This capacity to maintain high-performance characteristics at reduced sizes is crucial for evolving AI technologies, where each transistor’s efficiency and reliability play pivotal roles. Essentially, TMDs offer new possibilities for fabricating transistors that surpass traditional silicon in both function and potential, marking a significant evolution in semiconductor technology.

Previous Methods and Their Limitations

A key aspect of the group’s earlier method involved covering a silicon wafer with a very thin film of silicon dioxide patterned with tiny openings or pockets. Flowing a gas of atoms over this mask, they observed that atoms settled into the pockets as seeds, ultimately growing into a regular, single-crystalline form. Despite its potential, this method faced a notable limitation—it required operational temperatures of around 900 degrees Celsius. Such high temperatures posed a significant risk of damaging underlying circuitry, thus limiting the viability of the method for practical applications in AI hardware. These conditions necessitated a rethinking of the fabrication process to mitigate risk while retaining performance.

For AI hardware to integrate these advanced materials, the fabrication process must feasibly operate at temperatures below 400 degrees Celsius to protect existing circuitry. This temperature reduction is crucial for ensuring that beneath the surface, intricate pre-existing silicon circuitry remains unharmed. High temperatures could compromise the delicate structures essential for semiconductor performance. Hence, bridging this temperature gap without compromising material quality or performance presented a formidable challenge that Kim’s team set out to overcome. Their subsequent advancements sought to address these inherent limitations while capitalizing on the unique properties of TMDs.

Innovative Low-Temperature Fabrication Process

Inspiration from Metallurgy

The new approach detailed by Kim and his colleagues draws inspiration from metallurgy, specifically the process of nucleation, where molten metal poured into a mold forms grains that merge into a patterned crystal at relatively lower energies and temperatures, particularly at the edges of the mold. Applying this principle, the researchers managed to grow single-crystalline TMDs at temperatures as low as 380 degrees Celsius. This significant reduction in energy requirement was achieved by strategically depositing seeds at the edges of the silicon dioxide mask’s pockets, thereby adhering to the natural grain formation processes observed in metallurgy.

This ingenious adaptation of metallurgical principles to semiconductor fabrication represents a departure from traditional methods, demonstrating a creative cross-disciplinary application that bridges material science and semiconductor engineering. By leveraging the natural nucleation process, the team has made it possible to grow high-quality TMDs efficiently and reliably at much lower temperatures, thus preserving the integrity of the existing silicon-based circuitry. This methodological shift not only enhances the practicability and scalability of the fabrication process but also opens new avenues for integrating these advanced materials into current semiconductor infrastructures.

Successful Fabrication of Multilayered Chips

Further refining their innovative method, the researchers fabricated a multilayered chip featuring alternating layers of two different TMDs: molybdenum disulfide (MoS2) and tungsten diselenide (WSe2). Molybdenum disulfide emerges as a promising candidate for fabricating n-type transistors, while tungsten diselenide shows potential for p-type transistors, both of which are essential for conducting logic operations within semiconductor devices. Importantly, these two materials were grown in single-crystalline form directly on top of each other without requiring intermediate silicon wafers. This achievement marked a significant step forward in the practical application of multilayered semiconductor chips.

The ability to directly stack these materials without additional substrates effectively doubles the density of a chip’s semiconducting components. This includes metal-oxide semiconductor (CMOS) structures, which are fundamental to the functionality of modern logic circuits. Furthermore, the successful integration of n-type and p-type transistors within the same chip layer opens up new possibilities for constructing more efficient, high-performance semiconductor devices. This advancement could mean the creation of three-dimensional logic and memory chips where multiple layers communicate efficiently without facing the traditional hindrances of silicon-based 3D chip manufacturing processes.

Implications for AI Hardware and Beyond

Enhanced Efficiency and Performance

This new method effectively doubles the density of a chip’s semiconducting components, including metal-oxide-semiconductor (CMOS) structures, which are fundamental to modern logic circuitry. In practical terms, this could mean the creation of three-dimensional logic and memory chips with multiple layers communicating efficiently without the limitations of traditional silicon-based 3D chip manufacturing processes. Conventional methods necessitate drilling through silicon wafers, which limits the number of stackable layers, reduces vertical alignment resolution, and often curtails production yields. The new method overcomes these obstacles, offering a solution for stacking logic and memory layers with higher efficiency and performance.

The double density of semiconducting components within these chips stands to significantly enhance overall computational power and data processing speeds. The new method eliminates the need for intermediary silicon substrates, thereby facilitating more seamless and faster communication between chip layers. This advancement is particularly impactful for AI hardware, where processing efficiency and speed are of paramount importance. Increased component density coupled with improved communication capabilities within multilayered chips could mean faster and more efficient AI computation, enabling more complex algorithms and larger data sets to be handled more proficiently.

Practical Applications and Future Prospects

Traditional semiconductor fabrication methods have heavily depended on silicon wafers to produce high-quality, single-crystalline semiconducting elements. This dependency creates significant obstacles, especially for the development of three-dimensional stackable chips. Typically, each semiconductor layer demands a thick silicon base, which slows down communication and computation across layers. These silicon layers act like wide pillars, hindering the efficiency and speed of data processing. However, MIT’s new method tackles this issue directly by eliminating the need for silicon wafer substrates, allowing for direct contact between multiple semiconducting layers.

By removing the traditional silicon base, MIT’s innovative approach not only boosts computational efficiency but also facilitates more compact and lightweight chip designs. The absence of silicon substrates ensures a more seamless integration of layers, optimizing data flow between them. This breakthrough could revolutionize AI hardware, leading to devices that are incredibly powerful and efficient. The consequences of this advancement are profound, potentially launching a new era where laptops and wearable devices are as powerful as today’s supercomputers, with storage capacities akin to modern data centers.