In the rapidly advancing landscape of technology, the hunger for faster, more efficient, and secure computing power has reached unprecedented levels, particularly in the realm of artificial intelligence (AI) and machine learning (ML). For decades, traditional CPU architectures have relied on speculative execution, a technique that predicts operation outcomes to keep processing pipelines full and boost performance. Yet, as AI workloads grow increasingly complex, the cracks in this approach are becoming impossible to ignore. Energy waste from incorrect predictions, unpredictable performance swings, and critical security vulnerabilities have exposed the limitations of speculative designs. Enter deterministic CPUs, a pioneering innovation that promises to overhaul processor architecture by eliminating guesswork and delivering consistent, reliable results.

Picture a processor that operates with absolute certainty, scheduling every instruction with pinpoint accuracy rather than banking on risky predictions. This is the core idea behind deterministic CPUs, a breakthrough supported by newly issued U.S. patents. By adopting a time-based execution model, these processors ensure predictable performance, a vital asset for the data-intensive computations at the heart of modern AI and ML applications. The potential to sidestep the inefficiencies and risks of speculative execution positions this technology as a transformative force in high-performance computing (HPC).

The urgency for such a shift is evident as AI demands continue to escalate, often involving intricate vector and matrix operations that exacerbate the shortcomings of traditional CPUs. Performance variability and pipeline stalls are just the tip of the iceberg, with security flaws like Spectre and Meltdown adding another layer of concern. Deterministic CPUs aim to tackle these issues directly, offering not only speed but also stability and safety. This article explores the inner workings of this emerging architecture, delving into how it stands apart from conventional designs and why it could redefine the future of AI computing.

Breaking Down the Limitations of Traditional Designs

Unpacking the Challenges of Speculative Execution

Speculative execution, once a revolutionary concept in processor design, has become a double-edged sword in the context of modern computing demands, especially for AI and ML tasks. This approach, which anticipates the outcomes of operations like branch decisions to maintain pipeline activity, often falters when predictions go awry. The result is a cascade of inefficiencies—pipeline flushes that discard incomplete work, leading to significant energy waste and erratic performance. In AI applications, where workloads vary widely across datasets and problem sizes, these fluctuations can create bottlenecks, undermining the reliability needed for real-time processing or large-scale model training. The unpredictability of performance cliffs poses a persistent challenge for developers striving to optimize complex algorithms.

Beyond inefficiency, speculative execution has revealed alarming vulnerabilities that threaten data security in an era where breaches can be catastrophic. High-profile exploits such as Spectre and Meltdown have demonstrated how speculative designs can inadvertently expose sensitive information through side effects of incorrect predictions. For AI systems handling vast amounts of confidential data, such risks are untenable, pushing the industry to seek alternatives that prioritize safety without sacrificing speed. The inherent flaws in speculative models highlight the pressing need for a paradigm shift, particularly as computational demands grow more intricate and stakes rise higher in fields like autonomous systems and predictive analytics.

Energy and Scalability Barriers in Conventional CPUs

Energy consumption stands as another critical hurdle for speculative CPUs, especially given the power-hungry nature of AI and ML computations. Each misprediction not only delays processing but also squanders energy on discarded operations, a problem amplified by the irregular memory access patterns common in AI workloads. As data centers supporting AI applications grapple with soaring operational costs and environmental concerns, the inefficiency of traditional designs becomes a glaring issue. The inability to consistently utilize resources effectively limits the scalability of speculative CPUs, making it difficult to meet the growing needs of advanced neural networks and massive data processing tasks without incurring prohibitive expenses.

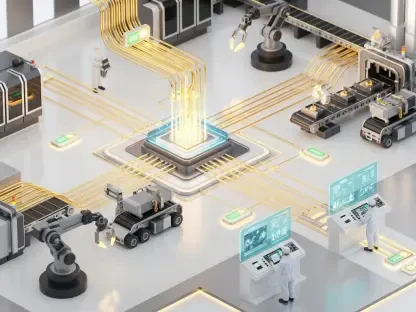

Moreover, the scalability constraints of speculative architectures often force reliance on specialized hardware like GPUs or Tensor Processing Units (TPUs) for AI workloads, adding complexity and cost to infrastructure. While these alternatives excel in specific scenarios, they lack the versatility of general-purpose CPUs, creating a fragmented ecosystem that can hinder seamless integration. The push for sustainable and cost-effective computing solutions has intensified the search for architectures that can balance high performance with energy efficiency. Addressing these barriers is not just a technical necessity but a strategic imperative for an industry racing to keep pace with the exponential growth of AI-driven innovation.

Exploring the Promise of Deterministic Architectures

Core Mechanics of Time-Based Execution

At the foundation of deterministic CPUs lies a radical departure from the speculative model, centering on a time-based execution framework that prioritizes precision over prediction. This innovative approach assigns specific execution slots to instructions using a cycle-accurate time counter, ensuring that each operation proceeds only when all necessary data dependencies are resolved. By eliminating the guesswork inherent in speculative designs, this method prevents the costly pipeline flushes that plague traditional CPUs. For AI and ML workloads, which often involve highly structured computations, this predictability translates into a steady performance profile, free from the erratic swings that disrupt efficiency. The deterministic model offers a streamlined flow, aligning perfectly with the need for consistent results in data-intensive environments.

The technical elegance of this design is evident in its ability to maintain high throughput without the baggage of speculative overhead. Unlike conventional processors that must constantly recover from incorrect predictions, deterministic CPUs orchestrate instruction dispatch through mechanisms like a register scoreboard, which tracks data availability with precision. This structured scheduling fills latency windows with productive work, a stark contrast to the wasted cycles of speculative missteps. In the context of AI tasks, where vector and matrix operations demand relentless computational power, such efficiency can significantly reduce processing times. The promise of deterministic execution lies in its capacity to deliver reliability without compromising on the raw performance needed for cutting-edge applications.

Architectural Innovations for AI Workloads

Deterministic CPUs build on familiar frameworks like the RISC-V Instruction Set Architecture (ISA), ensuring compatibility with existing programming tools while introducing groundbreaking features tailored for modern challenges. A key component, the Time Resource Matrix (TRM), sits between the fetch/decode stages and execution units, managing instruction dispatch with meticulous accuracy. This setup, combined with deep pipelines and wide front ends, preserves the throughput benefits of out-of-order execution but without the speculative inefficiencies. For AI and ML workloads, the inclusion of configurable General Matrix Multiply (GEMM) units—capable of handling a range of operand sizes—provides the flexibility to tackle diverse computational patterns, from small-scale models to sprawling neural networks.

Early evaluations of deterministic CPUs suggest a scalability that rivals specialized hardware like TPUs, but with notably lower power consumption and cost barriers. This could be a game-changer for industries seeking high-performance AI computing without the hefty investment in niche solutions. The architecture’s ability to maintain consistent behavior across varying workloads addresses the performance variability that often hampers speculative CPUs during complex calculations. Additionally, the energy savings achieved by avoiding wasted work align with the broader push for sustainable technology, making deterministic designs a compelling option for data centers powering AI innovation. The fusion of general-purpose versatility and AI-specific optimizations positions this technology as a potential cornerstone for future computing ecosystems.

Security and Developer Benefits

One of the standout advantages of deterministic CPUs is their inherent resistance to the security flaws that have plagued speculative architectures. By design, these processors avoid speculative operations, thereby eliminating the side effects that vulnerabilities like Spectre exploit to access sensitive data. In an era where AI systems process vast troves of personal and proprietary information, such robust security is non-negotiable. This architecture offers a safer foundation for applications ranging from healthcare diagnostics to financial forecasting, where data breaches can have devastating consequences. The absence of speculative risks not only protects end users but also reduces the burden on developers to implement complex safeguards against potential exploits.

From a programming perspective, deterministic CPUs introduce a level of predictability that simplifies software optimization for AI and ML tasks. Developers no longer need to account for the unpredictable behavior of speculative execution across different datasets or hardware configurations. The execution contract guarantees consistent dispatch and completion times, easing the process of compiler scheduling and reducing the need for workaround code to handle misprediction recovery. Compatibility with mainstream toolchains like GCC and LLVM further ensures a smooth transition, allowing teams to leverage existing skills while benefiting from enhanced performance stability. This streamlined development environment could accelerate the rollout of sophisticated AI solutions, fostering innovation across diverse sectors.

Future Implications for High-Performance Computing

Looking ahead, deterministic CPUs represent a potential paradigm shift in processor design, echoing the transformative impact speculative execution once had on the industry. While immediate replacement of traditional CPUs in all domains remains unlikely, the unique demands of AI and HPC workloads create a fertile ground for adoption. The ability to deliver high performance with reduced power and cost overhead positions this technology as a viable middle ground between general-purpose processors and specialized hardware. As data intensity continues to surge, the deterministic approach could pave the way for more accessible, efficient computing solutions, particularly for smaller organizations unable to invest in bespoke systems.

The broader implications for the tech landscape are worth considering as well. With recent patents validating the novelty and feasibility of deterministic designs, industry momentum may build toward integrating these architectures into mainstream platforms over the coming years, potentially from now through 2027 and beyond. This shift could spur a reevaluation of how performance, efficiency, and security are balanced in CPU design, influencing everything from cloud computing to edge devices powering AI at the point of use. While challenges in widespread implementation persist, the groundwork laid by deterministic CPUs suggests a future where computing power aligns more closely with the evolving needs of data-driven innovation, offering a glimpse of what’s possible when predictability takes center stage.