While the technology sector once measured progress through the sheer quantity of general-purpose chips available for rental, the unveiling of Google’s eighth-generation Tensor Processing Units signals a permanent shift toward radical architectural specialization. This movement reflects a broader market realization that the monolithic approach to artificial intelligence infrastructure has reached its physical and economic limits. As computational demands continue to outpace the growth of traditional silicon, the necessity for a more nuanced strategy has become the primary driver of innovation. The introduction of the 8th-gen TPU architecture is not merely an incremental upgrade but a structural reorganization designed to meet the divergent needs of the next decade of autonomous systems.

Tracing the Historical Evolution: From Commodity Silicon to Specialized Infrastructure

The current state of specialized hardware did not emerge in a vacuum; it is the result of a decadelong transition away from the standardized hardware models that once dominated the cloud. For a significant period, the industry operated under a paradigm where hardware was a neutral layer provided by a few key vendors, leaving software to do the heavy lifting of optimization. However, as the scale of data processing grew exponentially, the inherent inefficiencies of general-purpose processors became a visible bottleneck for the largest players. The historical decision by a handful of leaders to build proprietary silicon served as a foundational pivot point that allowed for a greater degree of control over technical destiny.

Understanding this background is essential for grasping why the market has reached its current inflection point. In the early stages of the AI boom, organizations were primarily focused on acquiring any available computational power, often paying a premium for hardware that was not perfectly suited for their specific workloads. This era of commodity-driven expansion has given way to an environment where the vertical integration of hardware and energy is the only viable method to maintain a competitive advantage. The shift highlights a broader industry trend where the successful deployment of frontier models is no longer just a software challenge but an intricate logistical problem involving specialized physical infrastructure.

A Strategic Pivot: The Bifurcation of Training and Inference

Scaling the Frontiers: The TPU 8t Training Engine

The introduction of the TPU 8t marks a significant departure from the tradition of releasing a single, multi-purpose chip for all tasks. This hardware is engineered specifically as a training powerhouse, designed to tackle the massive-scale workloads required for the most advanced models. By delivering 121 FP4 EFlops per pod, it offers a dramatic increase in performance compared to previous generations, focusing on the “wall-clock time” challenges that plague modern model development. The implementation of the Virgo networking interconnect is a critical component of this design, allowing clusters to scale beyond one million chips in a single environment. This level of scalability is necessary to overcome the diminishing returns seen in smaller, less integrated systems.

Optimizing for Interaction: The TPU 8i Inference Architecture

In contrast to the brute force of the training engine, the TPU 8i represents a specialized response to the needs of the agentic era where interaction and reasoning take precedence. This architecture is built to prioritize latency and memory bandwidth, which are the primary constraints for real-time model sampling. The development of the Boardfly topology has addressed the “network diameter” problem, minimizing the number of hops between chips to ensure that responses are as instantaneous as possible. This optimization is particularly beneficial for the iterative feedback loops required by modern reasoning models, where the delay of even a few milliseconds can disrupt the fluid execution of an autonomous agent.

Overcoming the Bottleneck: Managing Data Flow and Integrated Networking

A major challenge in the development of high-performance AI systems has always been the efficient movement of data across the network. The 8th-gen architecture addresses this through the implementation of TPU Direct Storage, which allows information to move from managed storage directly into High Bandwidth Memory without the traditional delays of CPU mediation. This innovation reduces the total hours required to complete training epochs and significantly lowers the operational costs for enterprise customers. By optimizing the data path, the architecture ensures that the computational cores are never left idle, maximizing the utility of every watt of power consumed by the data center.

Emerging Patterns: The Future of Integrated Compute and Orchestration

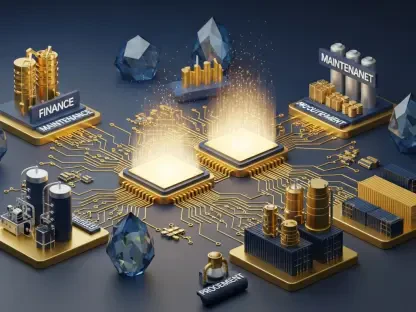

Looking at the trajectory of the market through the rest of the decade, it is clear that the focus is shifting away from raw transistor counts and toward architectural efficiency. The industry is moving into an era where general-purpose accelerators may no longer be the default choice for market leaders who demand extreme performance at scale. One notable trend is the revitalization of specialized CPUs, which are being repositioned not as primary calculators but as essential orchestration layers for agent sandboxes and tool execution. This creates a hybrid environment where different types of silicon work in tandem to manage the complex logic of future AI applications.

Furthermore, as regulatory and economic pressures continue to mount, the ability to provide predictable “cost-per-token” economics will become the most important metric for cloud adoption. Vertical integration is no longer an experimental strategy but a requirement for any provider wishing to offer competitive pricing in a crowded market. The companies that control the entire stack, from the physical energy source to the final software output, will be the ones that set the standard for the rest of the industry. This shift likely signifies a period of consolidation where infrastructure expertise becomes the primary barrier to entry for new competitors in the high-end model space.

Strategic Takeaways: Navigating the New Cloud Procurement Landscape

For decision-makers and technology leaders, the arrival of this specialized architecture necessitates a fundamental change in how cloud resources are evaluated. The criteria for procurement are moving beyond simple availability toward a deep alignment between hardware profiles and specific application needs. Organizations that are focused on training proprietary models must now prioritize the “goodput” of the system and the quality of the networking interconnects rather than just the number of GPUs. For those building real-time agents, the focus should instead be on memory capacity and the latency benchmarks that define the user experience.

Adapting to this new landscape also requires addressing the “portability friction” that exists when moving between different hardware ecosystems. While standardized environments offer ease of use, the performance gains and cost savings provided by specialized silicon like the TPU v8 often justify the engineering investment required to port workloads. The best practice for enterprise integration is to conduct rigorous testing of specific workloads across different architectural paths. This ensures that the chosen infrastructure not only supports the current needs of the business but also provides a scalable foundation for the increasingly complex reasoning tasks that define the modern landscape.

Redefining Innovation: The Long-Term Impact of Specialized Silicon

The debut of the 8th-gen TPU architecture established a new benchmark for how computational power is delivered to the global market. By moving to a dual-chip roadmap, the industry successfully addressed the growing divide between the requirements of model training and the demands of real-time inference. This transition proved that the era of the general-purpose AI chip was effectively over for those operating at the frontier of the technology. The development of specialized networking topologies like Boardfly and Virgo ensured that the underlying hardware did not become a bottleneck for the increasingly sophisticated software it was intended to support.

Ultimately, these advancements provided a clear path for enterprises to scale their operations without encountering the prohibitive costs associated with less efficient, third-party hardware. The move toward vertical integration allowed for a level of optimization that was previously impossible, creating a more sustainable economic model for the deployment of large-scale AI agents. As organizations integrated these new tools into their workflows, the focus shifted from the mere acquisition of compute to the strategic application of architectural advantages. The lessons learned from this transition served as the blueprint for the next generation of digital infrastructure, ensuring that the technology remained capable of supporting the most ambitious goals of human-AI collaboration.